長野実装フォーラム

Nagano Jisso Forum

3-1.半導体パッケージ

半導体パッケージには様々な材料が用いられ、様々な形状のものがある。半導体の初期から使われ、現在も使われているものから、一時の隆盛から姿を消したり、消しかけたりしているものもある。このようなことが起こるのはもちろん機能的な要求が大きいが、コスト的な要求も強く働いている。

3-1-1.TOヘッダー

TOヘッダーはトランジスターの実装の初期から使われたパッケージで、TOはTransistor Outline である。チップが載るパッドにリードが付き、樹脂封止されるものなど、いくつかの種類があるが、代表的なものは図3-1に示すようなキャンタイプの気密パッケージである。主にトランジスター、IC、ダイオードなどのパッケージに使用された。現在ではこのタイプの発展形のパッケージが各種のセンサーやLD(Laser Diode)用のパッケージとして使用されている。アイレット(金属部分)にはコバールが使用され、これに高融点ガラスタブレットの微小な穴にリードが挿入され、カーボン治具の中で組み立てられて、炉で溶着される。コバールはガラスとの溶着のため特別に開発された材料で、両者の熱膨張係数が同じになるように設計されている。このタイプのパッケージはマッチドタイプと言われ、高度な気密封止が可能になる。

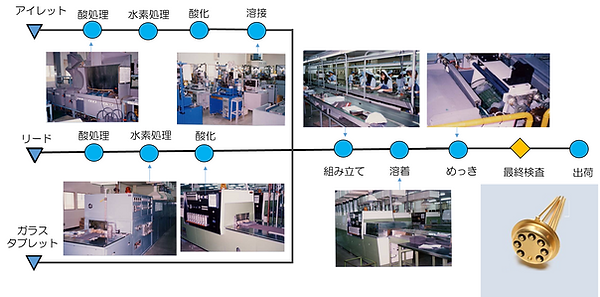

図3-1.TOヘッダーと各部材

下は基材と気密封止するためのガラスタブレット

TOヘッダーは、古いタイプのパッケージなので、現在は2社でしか製造されていない。しかしながら、その特徴はパッケージ内から外へのリークが1×10^{-10} atm・cc/sec という超高気密で、このレベルの気密性が得られる技術はほかにはないとされている。今では珍しい技術になっているので、図3-2にTOヘッダーの製造プロセスを示す。

図3-2.TOヘッダーの製造プロセス

このプロセスの一番の特徴は酸化工程にある。コバールに適度な厚みの酸化膜をつけることで、ガラスとコバールの相互拡散が起こり、高気密な溶着が達成される。これを図3-3に示す。

図3-3.ガラス‐コバールの溶着界面のTEM像

TOヘッダーはこのような高気密パッケージであるので繊細なトランジスターのパッケージとしては最高のチップ保護装置である。しかし、メサ型構造のトランジスターの場合、チップのPNP接合面が露出していたため、キャップの溶接時に飛び散った金属片がチップに付着し、ショート不良を起こし、大問題になったことがある。このため、チップの接合面が露出しないプレーナー構造のトランジスターが開発され、問題を解決したという歴史がある。こういうことから、その後、ICチップになっても、まずは新しい高機能チップは高気密で保護機能の高い気密パッケージに搭載されることとなった。

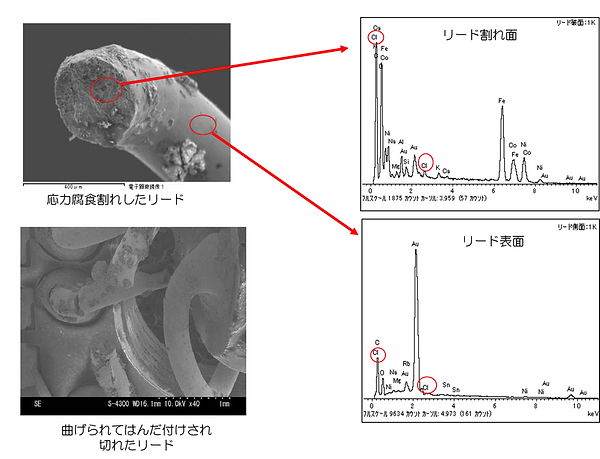

通常、チップボンドは金シリコンで行い、ワイヤーボンドはアルミ線を使用したマニュアルのウエッジボンディングが行われた。基板への実装はリードを極端に曲げてはんだ付けする場合もあり、応力腐食割れ(SCC: Stress Corrosion Cracking)が起こることもあった。この割れ部分には必ず塩化物イオン(Cl-)が検出され、同時にここは曲げなどで応力が発生している部分である。中々典型的な応力腐食割れの例が見られないため、フィールドで発生したSCCの例を図3-4に示す。しかし、このSCCが起こる完全なメカニズムはいまだわかっておらず、実験で条件をそろえ再現しようと試みても再現できていない。

図3-4.リードで発生した応力腐食割れ(SCC)

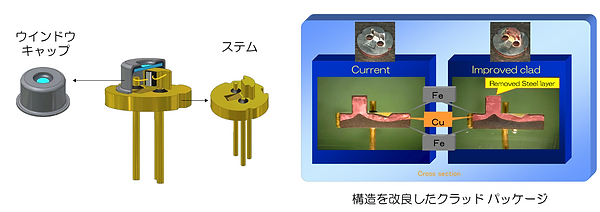

上記のパッケージに比べ気密度は劣るが、レーザーダイオード(LD: Laser Diode)に使用されるキャンタイプのパッケージがある。これはガラスとアイレットの熱膨張係数を調整して、溶着後に溶着部のガラスに圧縮応力がかかるように設計されている。アイレットは鉄で作られるほかに高放熱性を得るために、銅ブロックをロウ付けする。このブロック部分はチップを搭載するために面角度や平坦�性に高い精度が求められる。しかし、コスト面からの要請で図3-5に示すような銅クラッド材を用いたプレスによる成型も行われている。このアイレットの底面はリードを抵抗溶接する必要から鉄であることが求められ、このような材料が使用されている。TOヘッダーに用いられるコバール材は難加工性の材料なため、小さな穴の加工や絞り加工は難しい。LDパッケージの場合も、3mmもの高さのブロックを立ち上げる加工は難しい。現在ではこのような加工を行うためのシミュレーターが開発されており、このようなシミュレーターを使って、事前に工法を確認しながら技術確認をしないと目的とする加工法を見出すことは困難である。

図3-5.LDパッケージと加工例

3-1-2.セラミックパッケージ

セラミックパッケージはパッケージの構成材料をいう呼び方である。主なセラミックパッケージを図3-6,3-7に示す。多層、多ピンパッケージが可能で、キャビティ―を持ち、チップを気密封止することで、耐熱性や耐環境性に優れたパッケージが実現できる。したがって、1970年代の初めころまでは新しいチップは、まずセラミックパッケージに搭載され、十分な機能や特性が確認されたら、価格の安いモールド樹脂封止のパッケージに移行することが行われていた。。

図3-6.C-DIPとセラミックDIP

図3-7.多層高機能セラミックパッケージ

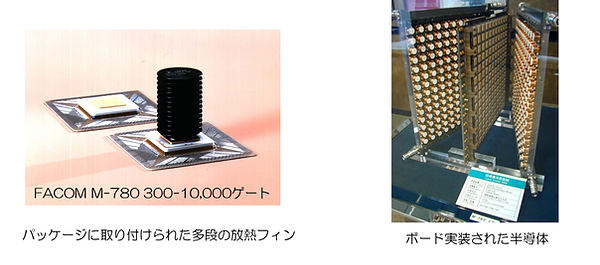

パッケージ形態ではDIP(Dual In-line Package)から多ピンのPGA(Pin Grid Array)やフラットパッケージもある。メインフレームコンピューターのECLチップを実装するのにも使われ、五重の塔のような放熱フィンをつけて放熱をはかった例もある。しかし、セラミックパッケージは高価なので、セラミックベースにリードフレームを低融点ガラスで溶着したコストの低いサーディップパッケージも使用された。

BGAはボード実装でのパッケージとボードの熱膨張差の吸収ができず、実際はほとんど使われなかった。材料としては主にアルミナが使用された。後に、より一層の高機能化を目指してムライト、炭化ケイ素(SiC)、窒化アルミニウムなど、様々な材料が検討されたが、最終的にはプリント基板を使用したパッケージに道を譲ることになった。

アルミナを使用した多層セラミックパッケージの製造プロセスを図3-8に示す。アルミナの粉末に焼結助剤のシリカ(SiO2)、カルシア(CaO)、マグネシア(MgO)を加え、アルミナ純度92%に調整する。これに溶剤と有機バインダー(結合剤)、可塑剤、分散剤を添加し、ボールミルによりスラリー(泥漿)を調整する。

図3-8.多層セラミックパッケージの製造プロセス

バインダーはセラミック粒子の分散・結合を行うもので、分散性,造膜性,柔軟性・靭性に優れていることが求められる。回路パターンの形成には、ア ルミナではタングステンが使われるので、この酸化を防ぐために焼成雰囲気は還元雰囲気に調整されている。そのため熱分解性が比較的良好なブチラール樹脂やアクリ ル樹脂が一般的に用いられている。可塑剤は、テープを柔軟で扱いやすいものにするために添加するもので、ジオクチルフタレートなどが使用される。分散剤は、アルミナ粉末がスラリー中に均一に分散することを助けるもので、テープに成型後に表裏の差が出にくいようにするためのものである。ガラス-アルミナ系の低温焼成基板のように、異なる2種の材料を分散調合するときには時に重要で、2つの材料の表面状態の違いが分散に影響を与えないようHLB(Hydrophilic-Lipophilic Balance)値を参考に選定する。

スラリーは、ドクターブレード法によりペットフィルム上にキャスティングし、これを乾燥して、グリーンシートとして巻き取る。このグリーンシートにタングステンペーストをスクリーン印刷して回路を形成する。

この様子を図3-9に示す。

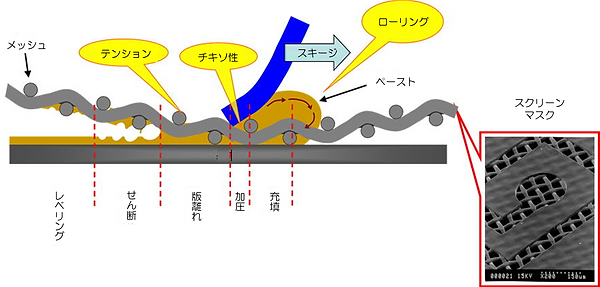

図3-9.スクリーン印刷

この際ペーストはスキージにより押し出されてスクリーンマスクを透過し、シートに印刷される。スクリーンはメッシュ状に金属の線が織られており、線の交差部は盛り上がっているため、乳剤を使ってのマスクつくりの精度の制約事項になる。また、線が太いとペーストの抜ける面積が小さくなる。このようなマスクの制約から、通常は線幅100μm程度が最小である。

次に、このシートを積層し、焼成する。焼成はその前にバインダーや可塑剤を除くバーンアウト工程を必要とするが、これを還元雰囲気で行うことになるので、分解が難しく、分解しやすい材料選びが重要である。焼成炉には還元雰囲気を作るために水蒸気やアンモニア分解ガスが導入される。

アルミナの場合、普通1600℃前後で焼成される。この際焼成収縮が起こるので、寸法を設計値通り仕上げること、反りを最小限に抑える技術が重要である。パッケージ用のアルミナはアルミナ純度92%のものが使用されるが、これは焼結の際にアルミナと焼結助剤がガラスを生成し、これが焼結を進めると同時にタングステン粒の粒間に入り込み、回路を密着良くセラミックス上に形成する必要があるためである。焼成後は無電解ニッケルめっきを行い、ピンをロウ付けし、ニッケル、金めっきをほどこして完成する。

3-1-3.セラミックパッケージの展開

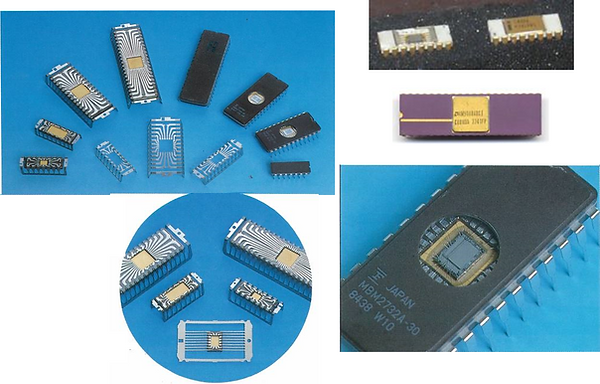

すでに述べたようにセラミックパッケージは多層配線が可能な高機能で高気密、ロバストなパッケージである。特にHAST (High Accelerated Stress Test)では、プリント基板など有機物のパッケージでは迫れない強みがある。また、窓付きの封止が可能であることからEPROM(Erasable Programmable Read Only Memory**)**のパッケージとしても使用された。

セラミックパッケージは主にマイクロプロセッサー(MPU)やASICなどに使用された。MPUの例を図3-10に示す。

図3-10.MPUの実装の進化

MPUはチップの進化とともにピン数が増加し、クロック周波数が高周波数化したのに伴い、DIPから多ピンが可能なPGAになった。また、高周波の信号が伝送し難くなってきたことから、80386の世代では分布定数回路の考え方で回路が設計されることになった。この場合、図3-11に示すように、132ピンPGAでパワー・グラウンド層4層、信号層2層で、信号配線の特性インピーダンス、インダクタンス、キャパシタンスが制御され、高�速信号がインテグリティを維持して伝送できることになった。

図3-11.セラミックパッケージの層構成

その後MPUは高機能、高速の道を突き進むことになったが、セラミックスの限界(高速、高機能対応)を超えるパッケージとしてプリント基板を使用したパッケージ、さらに微細配線のためにビルドアップ基板を使用したパッケージに展開されているが、回路設計には引き続きこの技術を進化させて使われている。この設計技術の基本に��なる回路技術を図3-12に示す。

図3-12.分布定数回路の基本技術

インテルのMPUの実装にはPentiumの第一世代まではセラミックPGAが使用された。しかし、タングステンによる回路は電気抵抗が大きく、またチップが大きくなってきたことから発熱量が大きくなり、チップとパッケージの熱膨張係数の違いによる膨張、収縮の差を吸収しきれなくなった。そこで、Pentium の第二世代からはプリント基板を使用したプラスチックPGAが使用されることになった。これにより配線パターンは銅で形成され、チップは基板のキャビティ―部に接着されたニッケルめっきした銅板に搭載されることになった。これには大型チップを銅に載せても熱膨張差を吸収できるチップボンド用の樹脂が開発されたことが大きく貢献している。

これは後述するが、先行したOMPAC(Overmolded Pad Array Carrier)でのペースト開発の成果によっている。このプリント基板パッケージの開発は、主としてコストの高いセラミックスを安いプリント基板に置き換えることを主眼に行われたものであるが、まず実現できたことは高機能パッケージであった。すなわち配線が銅に変わったことで、信号線の低抵抗化が実現され、チップが銅板に搭載されたことから、放熱効果が格段に高まったためである。チップをプラスチックパッケージに搭載することで、高速で動作するチップが断然多く取れ、高く売れたのである。セラミックパッケージの技術者の中にはセラミックパッケージの高気密、ロバスト、高信頼性を理由に、やわなプリント板に変わっても必ずセラミックスに戻ってくると主張した向きも多かったが、2、3世代下ったところで、プリント基板パッケージは当初の狙い通り、セラミックパッケージでは実現できない高機能、低コストパッケージを実現した。

さらに信号伝送方式に関して、最近では、より一層の高速・高周波信号の伝送に対応するため「差動信号伝送」方式が採用されてきている。差動信号伝送(ディファレンシャル伝送)は、1組の対 (ペア) になった伝送線路に信号を流す方式である。このときに位相が同じ信号(同極性)を扱うのを偶モード(even, 同相 モード)、位相が180度異なる信号(逆極性)を扱うのを奇モード(odd, 差動 モード)という。通常、差動伝送は奇モードであり、二本の配線で正・負極のデータを伝送する。

差動信号伝送には、次のような特徴・特長がある。

-

高速低振幅のLVDS (low voltage differential signaling)回路に適する

-

外来ノイズに対して強い

-

グラウンドの影響が少ない

-

不要輻射ノイズ (EMI: electromagnetic interference) が少ない

-

高速性に富む

-

信号伝送の安定性が高い

-

消費電力が低い

高価セラミックパッケージの例に1995年に発売されたPentium proがある。これを図3-13に示す。

図3-13.Pentium pro

Pentium ではキャッシュからのデータ伝送が間に合わなくなり、マザーボードとは別に二次キャッシュ専用のバスを設け、これをCPUと同じパッケージに搭載したために大きなパッケージになった。

このため、CPUと同じ速度の二次キャッシュは実現できたが、製造が難しく、高価なものになった。2次キャッシュが256 KB、512 KBのものは紫色のセラミックスに、写真のように金色に輝くヒートスプレッダがはめ込まれていた。これは値段の安さで売っていた他社と比べれば、その性能を誇示する豪奢さが際立つものであった。技術的には現在のチップレットに通ずるものであるが、当時の基板の回路技術からは困難な技術チャレンジであった。

上記のように、セラミックパッケージに求められる特性は、高機能でロバストなパッケージであることから、チップとの熱膨張係数が近いもの、熱伝導性が高く、放熱特性がすぐれているもの、配線抵抗が小さく、銅、銀での配線が可能なもの、高速信号の伝送特性がすぐれた低誘電率、低誘電体損出材料であること、へと移っていった。しかしながら、プリント基板を用いたパッケージでこれらの必要な特性が満足できることが確認されてからは、急速にセラミックスに対する興味は失われていった。

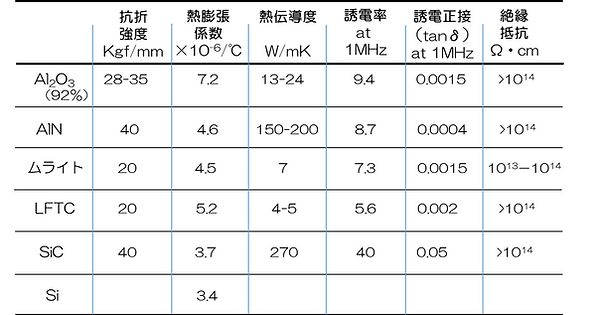

しかし、ここではこの時点で検討された種々のセラミック材料の特性を記すことにする。これを表3-1、図3-16に示す。

表3-1.各種セラミック材料の物性

図3-16.各種セラミックスの信号の伝搬遅延

これよりわかるようにアルミナはバランスのいい材料であるが熱膨張係数が大きいこと、熱伝導率が十分でないこと、AlNは熱伝導性に優れているが人工材料のため、また1800℃を超える高温での焼成が必要でコストが高いこと、ムライトは熱膨張係数はいいとしても、熱伝導性が低いこと。

低温焼成セラミックス(LFTC)は誘電率が低く、熱膨張係数も低いが、強度が弱いこと。また、銅パターンの同時焼成技術が難しいこと。SiCは熱伝導率は大きい(270W/mK)が、誘電率が大きいこと、などいずれもそれだけではパッケージとしての十分な特性が得られない。熱の問題に関してはアルミナに銅タングステン(CuW)をキャビティ―部にロウ付けしたものなど、実用化されたものもあるが、プリント基板パッケージに比べるとコスト的に太刀打ちできず、ビルドアップ基板のような微細配線もペーストの印刷では十分に対抗できない。したがって、技術的にセラミックスでは1GHzの壁を超えることができなかった。

しかし、セラミックパッケージの果たした役割は大きく、特にメインフレームコンピューターに使用されたECL(エミッタ結合論理:Emitter-coupled logic, ECL)ロジックチップはその時々の最先端チップであり、最先端の高密度配線セラミックパッケージが使われてきた。発熱も大きく、放熱、冷却についても先端技術が使用され、高機能な水冷システムが採用されている。多数のパッケージが搭載された基板はラックに収容され、一次、二次、三次の実装の姿が見られるので、これを図3-17に示す。

図3-17.メインフレームコンピューターに使われたセラミックパッケージ